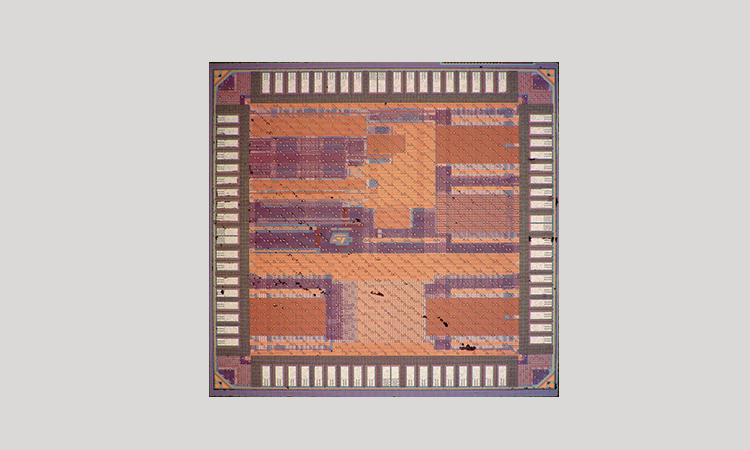

Chip Gallery SRAM

Designers:

Lauren Jones, Seng Oon Toh, Jason Tsai, Zheng Guo, Lynn Wang, Patrick Bennett and Kyoohyun Noh

Tapeout:

TSMC 45nm, December 2008

Description:

TThe SRAM Variability test chip is being designed to exercise memory and other 45nm blocks. SRAM experiments include bitline current measurements and WL/BL sweep capability, variation sensing and compensation circuits, dynamic read and write test structures to correlate with static metrics and wordline pulse generator to correlate required pulse widths with static metrics. Other experiments include parameter specific ring oscillators to characterize layout induced variability and ring oscillators with vias to the chip surface to test carbon nanotube delays.

Related publications:

IEDM 2009