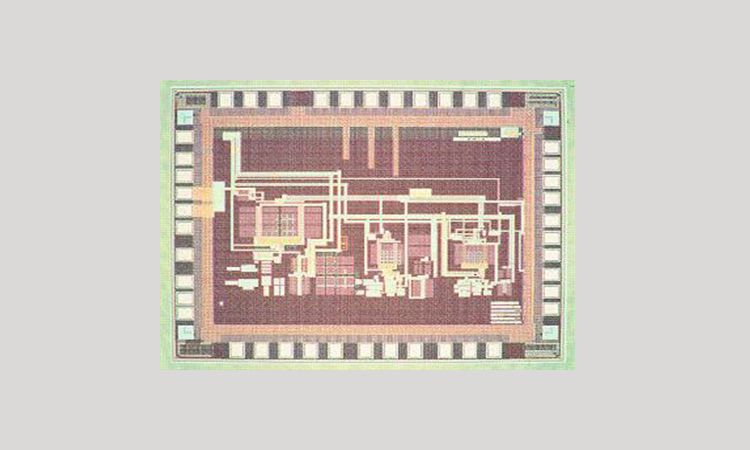

Chip Gallery 2-1 MASH ΣΔ

Designers:

Bill Tsang

Tapeout:

ST 130nm, June 2005

Description:

A 2.5V sigma-delta modulator with 97-dB peak SFDR and 82-dB peak SNDR at 1MS/s fabricated in 130-nm standard digital CMOS process. Chip dissipates 11 mW while running at 64 MHz clock frequency.

Related publications:

VLSI 2006