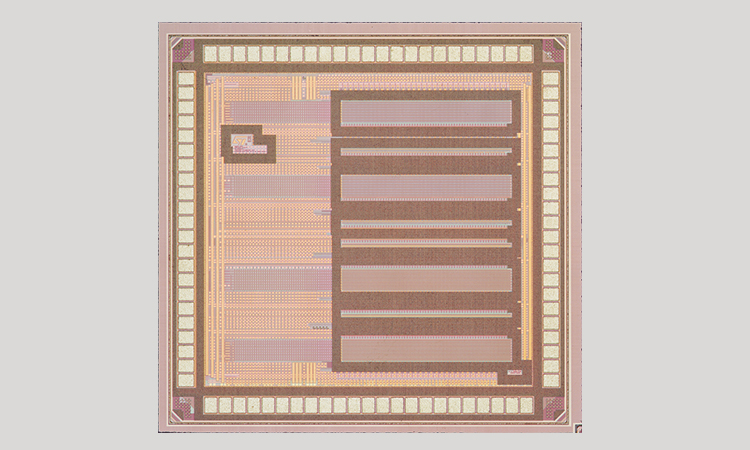

Chip Gallery Maskless Litho Chip

Designers:

David Fang

Tapeout:

ST 90nm, July 2005

Description:

A parallel, 12um-pitch, low-power 6-b segmented digital-to-analog converter (DAC) array drives an array of 3um x 3um analog DRAM cells in a 2.5/1V 90 nm CMOS process, with an application in maskless lithography. A self-calibrating compensation circuit limits the effect of charge leakage and capacitive process mismatch to less than 0.5LSB over 100ms of data hold time. A 2mm x 2mm test chip implements a mixed-signal interface with 32 DACs driving four 32 × 256 analog DRAM arrays.