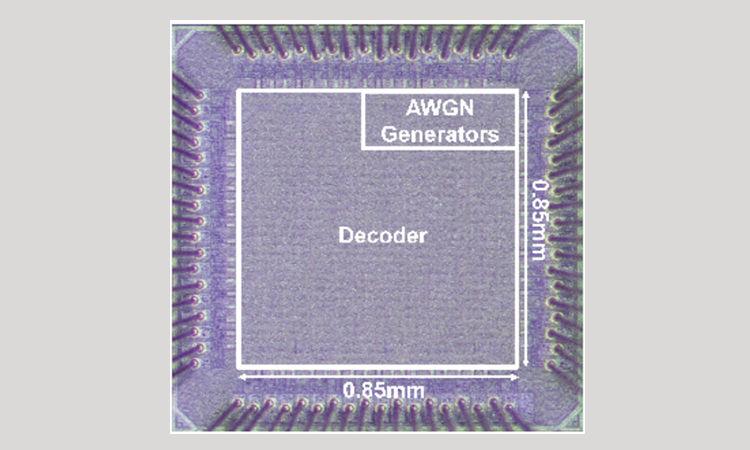

Chip Gallery LDPC

Designers:

Matt Weiner

Tapeout:

ST 28nm FDSOI, September 2013

Description:

The IEEE 802.11ad standard for Gb/s wireless LANs in the 60GHz band requires an implementation of an LDPC encoder/decoder with throughputs of 1.5, 3, and 6Gb/s, with code rates of 1/2, 5/8, 3/4 and 13/16. This chip implements a fully compatible IEEE 802.11ad LDPC decoder in 28nm ultra-thin body and BOX fully depleted SOI (UTBB FDSOI) technology with a power consumption that is a small fraction of the total baseband power. Previous implementations of decoders for these throughputs and levels of reconfiguration have power consumptions on the order of the rest of the baseband processing.

Related publications:

ISSCC 2014